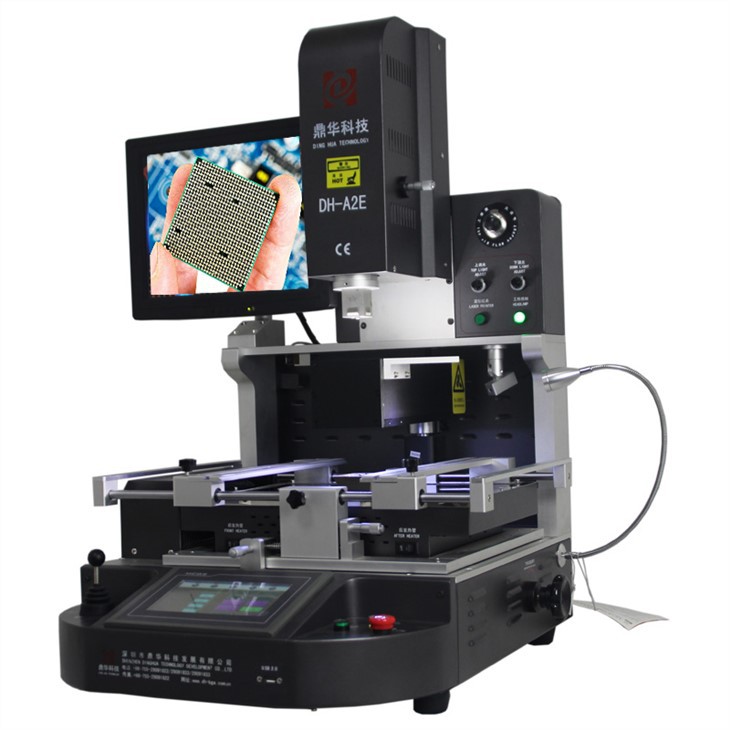

Auto Optical BGA Rework Station

Široce se používá při opravách na úrovni čipů pro základní desky mobilů, notebooků, počítačů, TV, klimatizací atd. Má vysokou úspěšnost oprav a vysoký stupeň automatizace a ušetří spoustu lidského úsilí. Jsme profesionální výrobce tohoto stroje a máme tyto stroje skladem.

Popis

Auto Optical BGA Rework Station

1. Aplikace Auto Optical BGA Rework Station

Základní deska počítače, chytrého telefonu, notebooku, logická deska MacBook, digitální fotoaparát, klimatizace, TV a další elektronické

zařízení z lékařského průmyslu, komunikačního průmyslu, automobilového průmyslu atd.

Vhodné pro různé druhy čipů: BGA,PGA,POP,BQFP,QFN,SOT223,PLCC,TQFP,TDFN,TSOP,PBGA,CPGA,LED čip.

2. Vlastnosti produktu Auto Optical BGA Rework Station

• Vysoká úspěšnost oprav na úrovni třísek. Proces odpájení, montáže a pájení je automatický.

• Přesné vyrovnání každého pájeného spoje lze zaručit pomocí optické vyrovnávací CCD kamery.

•Přesnou regulaci teploty lze zajistit pomocí 3 nezávislých topných oblastí. Stroj umí nastavit a uložit

1 milion teplotního profilu.

• Vestavěné vakuum v montážní hlavě automaticky nasbírá BGA čip po dokončení odpájení.

3. Specifikace Auto Optical BGA Rework Station

4. Podrobnosti o automatické optické BGA Rework Station

CCD kamera (přesný systém optického zarovnání); 2.HD digitální displej; 3. Mikrometr (nastavení úhlu čipu);

4.3 nezávislá topidla (horkovzdušná a infračervená); 5. Laserové polohování; 6. HD rozhraní dotykové obrazovky, ovládání PLC;

7.LED světlomet; 8. Ovládání joystickem .

5. Proč si vybrat naši automatickou optickou BGA Rework Station?

6.Certificate of Auto Optical BGA Rework Station

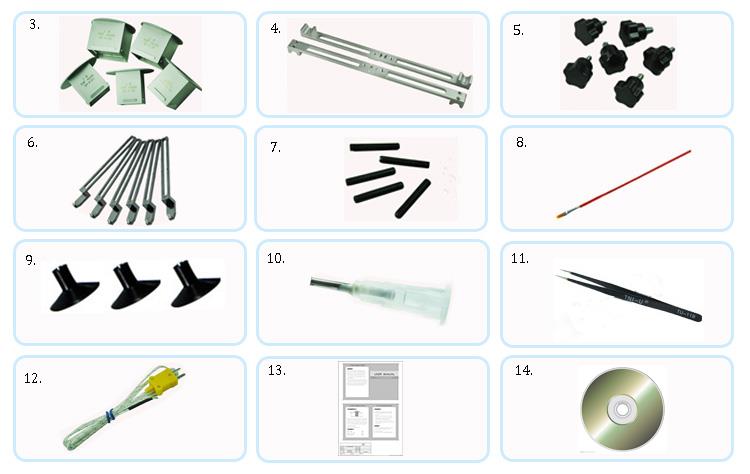

7. Balení a expedice Auto Optical BGA Rework Station

8.FAQ

Jak otestovat čip?

Počáteční test čipu na úrovni systému

SoC je založeno na hlubokých submikronových procesech, takže testování nových Soc zařízení vyžaduje zcela nový přístup. Protože každá funkční součástka

má své vlastní požadavky na testování, konstruktér musí vytvořit plán testování na začátku procesu návrhu.

Musí být implementován plán testování blok po bloku pro zařízení SoC: správně nakonfigurované nástroje ATPG pro testování logiky; krátké zkušební doby; nová vysokorychlostní

modely poruch a testy více pamětí nebo malých polí. U výrobní linky diagnostická metoda nejen najde chybu, ale také ji oddělí

vadný uzel z pracovního uzlu. Kromě toho by měly být použity techniky multiplexování testů, kdykoli je to možné, aby se ušetřil čas testování. V oblasti vysoce

integrované testování IC, testovatelné konstrukční techniky ATPG a IDDQ mají výkonný mechanismus separace chyb.

Mezi další skutečné parametry, které je třeba předem naplánovat, patří počet kolíků, které je třeba naskenovat, a velikost paměti na každém konci kolíku.

Hraniční skeny mohou být zabudovány do SoC, ale nejsou omezeny na testy propojení na deskách nebo vícečipových modulech.

I když se velikost čipu zmenšuje, čip může stále obsahovat miliony až 100 milionů tranzistorů a počet testovacích režimů se zvýšil na nebývalou úroveň.

úrovně, což má za následek delší testovací cykly. Tento problém lze otestovat. Chcete-li vyřešit režim komprese, kompresní poměr může dosáhnout 20 až 60 procent. Pro dnešní velkoplošné

návrhu čipu, aby se předešlo problémům s kapacitou, je nutné najít testovací software, který lze spustit na 64-bitových operačních systémech.

Kromě toho se testovací software potýká s novými testovacími problémy způsobenými hlubokými submikronovými procesy a rostoucí frekvencí. V minulosti byl testovací režim ATPG pro

testování poruch statického blokování již nebylo použitelné. Přidání funkčních vzorů k tradičním nástrojům ztěžovalo hledání nových chyb. Lepší přístup je k

klasifikujte minulé skupiny funkčních režimů, abyste určili, které poruchy nelze detekovat, a poté vytvořte režim ATPG pro zachycení těchto chybějících typů poruch.

Jak se zvyšuje konstrukční kapacita a zkracuje se doba testování na tranzistor, za účelem nalezení problémů souvisejících s rychlostí a ověření časování obvodu, synchronní testovací metoda

musí být zaměstnán. Synchronní testování musí zahrnovat více modelů poruch, včetně přechodných modelů, zpoždění cest a IDDQ.

Některé společnosti v oboru se domnívají, že nejúčinnější testovací strategií může být kombinace blokovacích, funkčních a přechodných poruch/zpoždění cesty. Pro hluboké

submikronové čipy a vysokofrekvenční provoz, testování přechodových jevů a zpoždění cesty je ještě důležitější.

Pro vyřešení problému přesnosti ATE při synchronizaci testovacího jádra a snížení nákladů je nutné najít novou metodu, která zjednoduší rozhraní

testovací zařízení (test přechodových jevů a zpoždění cesty vyžaduje přesné hodiny na rozhraní testovacího zařízení), zajišťuje, že signál je během testu dostatečně přesný.

Protože existuje vysoká možnost výrobních vad v bloku paměti SoC, musí mít paměť BIST diagnostickou funkci. Jakmile je nalezen problém,

vadná adresní jednotka může být mapována do redundantní paměti náhradní adresní jednotky a zjištěná chybová adresa bude vyřazena. Vyhněte se vyhazování

celý drahý čip.

Testování malých bloků vestavěné paměti eliminuje potřebu dalších hradel nebo řídicí logiky. Převádět lze například techniky testování převodu vektorů

funkční režimy do řady režimů skenování.

Na rozdíl od metody BIST nevyžaduje funkční vstup bloku paměti bypassu další logiku. Protože není vyžadována žádná další testovací logika, SoC

vývojoví inženýři mohou znovu použít testovací vzory, které byly vytvořeny v minulosti.

Pokročilé nástroje ATPG nejen paralelně testují makra, ale také určují, zda existují konflikty, a také podrobně popisují, která makra lze testovat paralelně a která

makra nelze testovat paralelně. Navíc lze tato makra efektivně testovat, i když jsou hodiny makra stejné jako hodiny skenování (jako je synchronní paměť).

V současné době není na husté oboustranné desce dostatek testovacích bodů a každý složitý čip musí být vybaven obvodem boundary scan. Bez

hraniční skeny, vyhledávání výrobních vad na úrovni desky je poměrně obtížné a nelze je ani najít. S boundary scan je testování na úrovni desky extrémně snadné

a nezávislý na logických obvodech v čipu. Boundary scan může také nakonfigurovat režim ATPG pro skenovací řetězec čipu v jakékoli fázi výroby.